# Introduction to Physical Electronics

**License: Creative Commons**

# Introduction to Physical Electronics

**By:** Bill Wilson

# Introduction to Physical Electronics

By:

Bill Wilson

### Online:

< http://cnx.org/content/col10114/1.4/ >

CONNEXIONS

Rice University, Houston, Texas

This selection and arrangement of content as a collection is copyrighted by Bill Wilson. It is licensed under the Creative Commons Attribution 1.0 license (http://creativecommons.org/licenses/by/1.0). Collection structure revised: September 17, 2007 PDF generated: October 25, 2012 For copyright and attribution information for the modules contained in this collection, see p. 247.

## Table of Contents

| 1 | Conduc                                    | ctors, Semiconductors and Diodes                                                                                                                                     |                                                                                      |

|---|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|   |                                           | Diffusion Light Emitting Diode LASER                                                                                                                                 | $egin{smallmatrix} . 5 \ 11 \ 18 \ 20 \ 25 \ 28 \ 33 \ 40 \ 43 \ 47 \ \end{bmatrix}$ |

| 2 | Bipolar                                   | Transistors                                                                                                                                                          |                                                                                      |

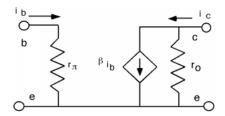

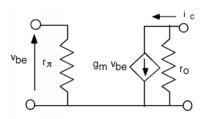

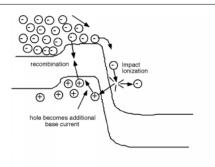

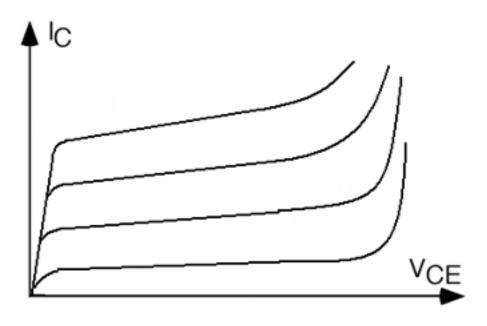

|   | _                                         | Intro to Bipolar Transistors Transistor Equations Transistor I-V Characteristics Common Emitter Models Small Signal Models Small Signal Model for Bipolar Transistor | 57<br>58<br>61<br>62                                                                 |

| 3 | $\mathbf{FETs}$                           |                                                                                                                                                                      |                                                                                      |

|   | 3.1                                       | Introduction to MOSFETs                                                                                                                                              | 71                                                                                   |

|   | 3.2                                       | Basic MOS Structure                                                                                                                                                  |                                                                                      |

|   | 3.3                                       | Threshold Voltage                                                                                                                                                    |                                                                                      |

|   | $\bf 3.4$                                 | MOS Transistor                                                                                                                                                       |                                                                                      |

|   | 3.5                                       | MOS Regimes                                                                                                                                                          |                                                                                      |

|   | 3.6                                       | Plotting MOS I-V                                                                                                                                                     |                                                                                      |

|   | $\begin{array}{c} 3.7 \\ 3.8 \end{array}$ | Models                                                                                                                                                               |                                                                                      |

|   | 3.9                                       | Inverters and Logic                                                                                                                                                  |                                                                                      |

|   | 3.10                                      |                                                                                                                                                                      |                                                                                      |

|   | 3.11                                      | JFET                                                                                                                                                                 |                                                                                      |

|   | 3.12                                      |                                                                                                                                                                      |                                                                                      |

| 4 | IC Mai                                    | nufacturing                                                                                                                                                          |                                                                                      |

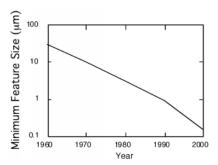

|   | 4.1                                       | Introduction to IC Manufacturing Technology                                                                                                                          | 15                                                                                   |

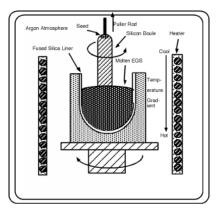

|   | 4.2                                       | Silicon Growth                                                                                                                                                       |                                                                                      |

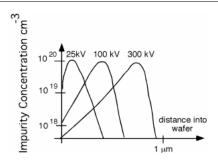

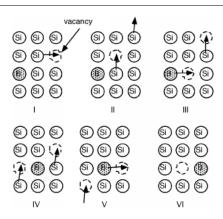

|   | 4.3                                       | Doping                                                                                                                                                               | 18                                                                                   |

|   | 4.4                                       | Fick's First Law                                                                                                                                                     | 20                                                                                   |

|   | 4.5                                       | Fick's Second Law                                                                                                                                                    |                                                                                      |

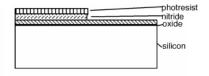

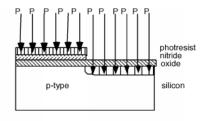

|   | 4.6                                       | Photolithography                                                                                                                                                     |                                                                                      |

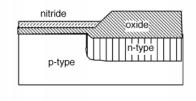

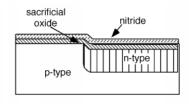

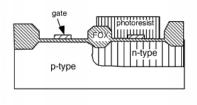

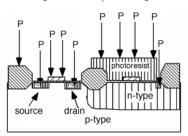

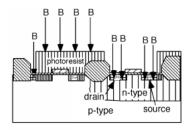

|   | 4.7                                       | Integrated Circuit Well and Gate Creation                                                                                                                            |                                                                                      |

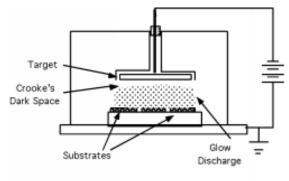

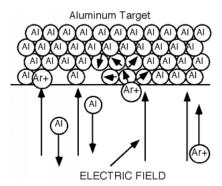

|   | 4.8                                       | Applying Metal/Sputtering                                                                                                                                            |                                                                                      |

|   | 4.9 $4.10$                                | Integrated Circuit Manufacturing: Bird's Eye View                                                                                                                    |                                                                                      |

|   |                                           | Vield 1                                                                                                                                                              |                                                                                      |

| Sol      | ıtions                                                     | 141 |

|----------|------------------------------------------------------------|-----|

| 5 Introd | luction to Transmission Lines                              |     |

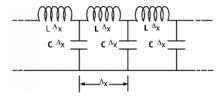

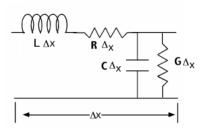

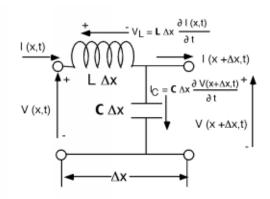

| 5.1      | Introduction to Transmission Lines: Distributed Parameters | 143 |

| 5.2      | Telegrapher's Equations                                    |     |

| 5.3      | Transmission Line Equation                                 | 148 |

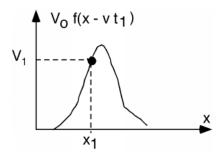

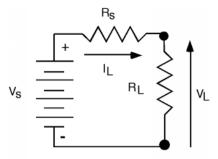

| 5.4      | Transmission Line Examples                                 | 151 |

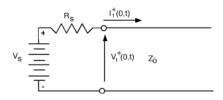

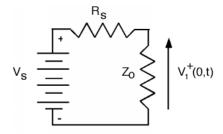

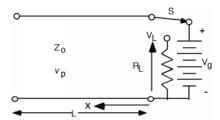

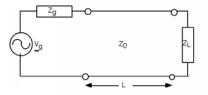

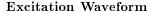

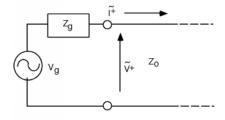

| 5.5      | Exciting a Line                                            | 153 |

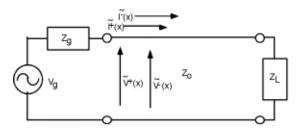

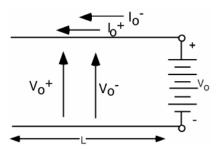

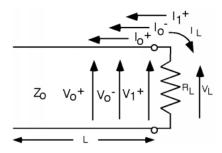

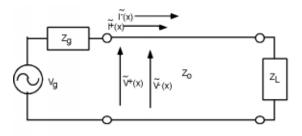

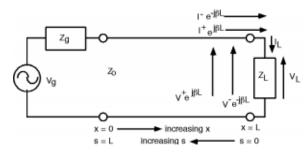

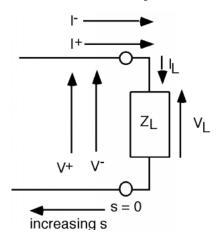

| 5.6      | Terminated Lines                                           | 156 |

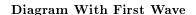

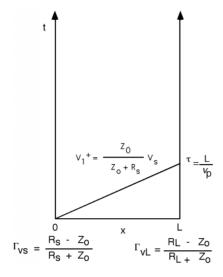

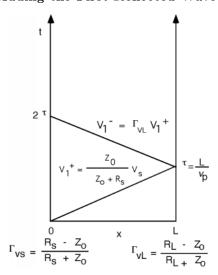

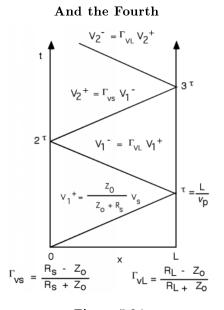

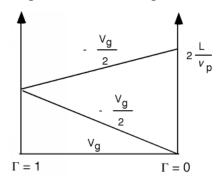

| 5.7      | Bounce Diagrams                                            | 159 |

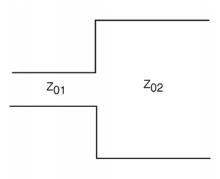

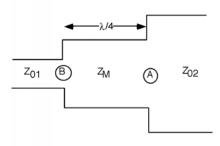

| 5.8      | Cascaded Lines                                             | 169 |

| Sol      | ıtions                                                     | 179 |

| 6 AC St  | eady-State Transmission                                    |     |

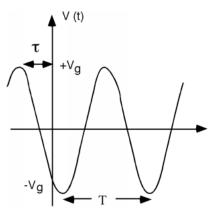

| 6.1      | Introduction to Phasors                                    | 181 |

| 6.2      | A/C Line Behavior                                          | 183 |

| 6.3      | Terminated Lines                                           | 186 |

| 6.4      | Line Impedance                                             | 189 |

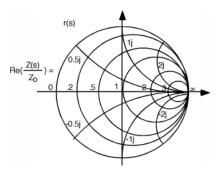

| 6.5      | Crank Diagram                                              | 189 |

| 6.6      | Standing Waves/VSWR                                        | 193 |

| 6.7      | Bilinear Transform                                         | 196 |

| 6.8      | The Smith Chart                                            | 200 |

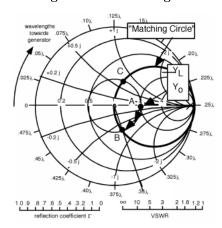

| 6.9      | Introduction to Using the Smith Chart                      | 211 |

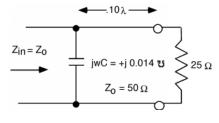

| 6.1      | O Simple Calculations with the Smith Chart                 | 212 |

| 6.1      | 1 Power                                                    | 216 |

| 6.1      | 2 Finding ZL                                               | 218 |

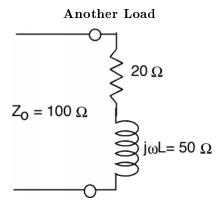

| 6.1      | <b>3</b> Matching                                          | 222 |

| 6.1      | 4 Introduction to Parallel Matching                        | 225 |

| 6.1      | 5 Single Stub Matching                                     | 226 |

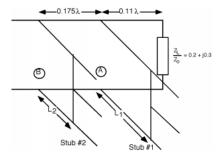

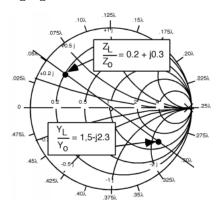

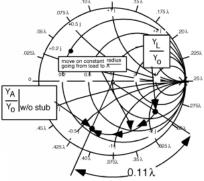

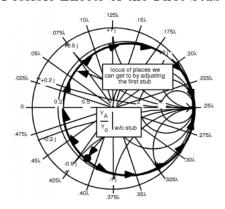

| 6.1      | 6 Double Stub Matching                                     | 230 |

| 6.1      | 7 Odds and Ends                                            | 237 |

| Glossary | ,                                                          | 242 |

| Index .  |                                                            | 243 |

| Attribut | ions                                                       | 247 |

## Chapter 1

# Conductors, Semiconductors and Diodes

### 1.1 Simple Conduction<sup>1</sup>

Our initial studies will more or less be a review of topics in electricity that you may have seen before in physics. However, if experience is any guide, there is no great harm in going back over this material, for it seems that for many students, the whole concept of just how electricity actually works is just a little hazy. Considering that you hope to be called an electrical engineer one of these days, this might even be a good thing to know!

Most of the "laws" of how electricity behaves are really just mathematical representations of a number of empirical observations, based on some assumptions and guesses which were made in attempt to bring the "laws" into a coherent whole. Early investigators (Faraday, Gauss, Coulomb, Henry etc....all those guys) determined certain things about this strange "invisible" thing called electricity. In fact, the electron itself was only discovered a little over 100 years ago. Even before the electron itself was observed, people knew that there were two kinds of electric charge, which were called **positive** and **negative**. Like charges exhibit a repulsive force between them and opposite charges attract one another. This force is proportional to the product of the absolute value of positive and negative charge, and varies inversely with the square of the distance between them. Different charge carriers have different mass, some are very light, and others are significantly heavier. Electrical charges can experience forces, and can move about. Since force times distance equals work, a whole system of energy (**potential** as well as **kinetic**) and energy loss had to be described. This has lead to our current system of electrostatics and electrodynamics, which we will not review now but bring up along the way as things are needed.

Just to make sure everyone is on the same footing however, let's define a few quantities now, and then we will see how they interact with one another as we go along.

The total charge in some region is defined by the symbol Q and it has units of Coulombs. The fundamental unit of charge (that of an electron or a proton) is symbolized either by a little q or by e. Since we'll use e for other things, in this course we will try to stick with q. The **charge of an electron**, q, has a value of  $1.6 \times 10^{-19}$  Coulombs.

Since charge can be distributed throughout a region with varying concentrations, we will also talk about the **charge density**,  $\rho(\nu)$ , which has units of  $\frac{\text{Coulombs}}{\text{cm}^3}$ . (In this book, we will use a modified MKS system of units. In keeping with most workers in the solid-state device field, volume will usually be expressed as a cubic centimeter, rather than a cubic meter - a cubic meter of silicon is just far too much!) In most cases, the charge density is not uniform but is a function of where we are in space. Thus, when we have  $\rho(\nu)$  distributed throughout some volume, V

$$Q = \int \rho(\nu) \, d\nu \tag{1.1}$$

describes the total charge in that volume.

$<sup>^{1}</sup> This\ content\ is\ available\ online\ at\ < http://cnx.org/content/m1000/2.21/>.$

We know that when we apply an electric field to a charge that there is a force exerted on it, and that if the charge is able to move it will do so. The motion of charge gives rise to an **electric current**, which we call I. The current is a measure of how much charge is passing a given point per unit time ( $\frac{\text{Coulombs}}{\text{second}}$ ).

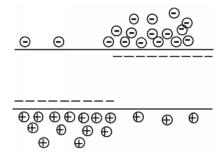

It will be helpful if we have some kind of model of how electricity flows in a conductor. There are several approaches which one can take, some more intuitive than others. The one we will look at, while not correct in the strictest sense, still gives a very good picture of how electrical conduction works, and is perfectly fine to use in a variety of situations. In the **Drude theory** of conduction, the initial hypothesis consists of a solid, which contains mobile charges which are free to move about under the influence of an applied electric field. There are also fixed charges of polarity opposite that of the mobile charges, so that everywhere within the solid, the net charge density is zero. (This hypothesis is based on the model of the atom, with a positively charged nucleus and negatively charged electrons surrounding it. In a solid, the atoms are fixed in position in the lattice, but it is assumed that some of the electrons can break free of their "host" atom and move about to other places within the solid.) In our model, let us choose the polarity of the mobile charges to be positive; this is not usually the case, but we can avoid a lot of "minus ones" this way, and have a better chance of ending up with the right answer in the end.

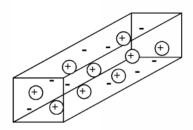

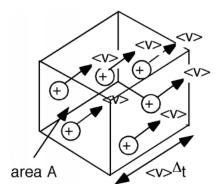

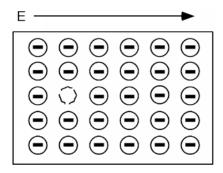

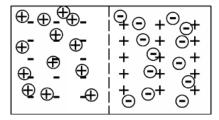

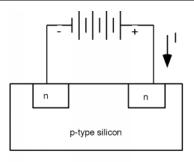

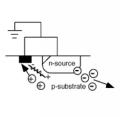

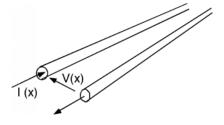

Figure 1.1: Model of a conductor.

As shown in Figure 1.1, the model of the conductor consists of a number of mobile positive charges (represented by the balls with the "+" sign in them) and an equal number of fixed negative charges (represented by the bare "-" sign). In subsequent figures, we will leave out the fixed charge, since it can not contribute in any way to the conduction process, but keep in mind that it is there, and that the total net charge is zero within the material. Each of the mobile charge carriers has a mass, m, and an amount of charge, q.

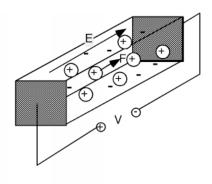

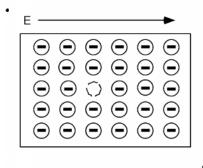

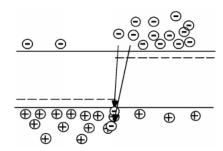

Figure 1.2: Applying a potential to a conductor

In order to have some conduction, we have to apply a potential or voltage across the sample (Figure 1.2). We do this with a battery, which creates a potential difference, V, between one end of the sample and the other. We will make the simplest assumption that we can, and say that the voltage, V, gives rise to a uniform electric field within the sample. The magnitude of the electric field is given simply by

$$E = \frac{V}{L} \tag{1.2}$$

where L is the length of the sample, and V is the voltage which is placed across it. (In truth, we should be showing E as well as subsequent forces etc. as vectors in our equations, but since their direction will be obvious, and unambiguous, let's keep things simple, and just write them as scalers.) **Electric potential**, or voltage, is just a measure of the change in potential energy per unit charge going from one place to another. Since energy, or work is simply force times distance, if we divide the energy per unit charge by the distance over which that potential exists, we will end up with force per unit charge, or electric field, E. If you are not sure about what you just read, write it out as equations, and see that it is so.

The electric field will exert a force on the movable charges (And the fixed ones too for that matter, but since they can not go anywhere, nothing happens to them). The force is given simply as the product of the electric field strength times the charge

$$F = qE \tag{1.3}$$

The force acts on the charges and causes them to accelerate according to Newton's equations of motion

$$F = m \frac{dv(t)}{dt}$$

$$= qE$$

(1.4)

or

$$\frac{d}{dt}v\left(t\right) = \frac{qE}{m}\tag{1.5}$$

Thus, the velocity of a particle with no initial velocity will increase linearly with time as:

$$v\left(t\right) = \frac{qE}{m}t\tag{1.6}$$

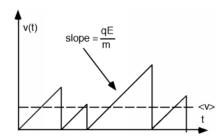

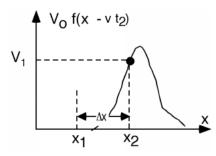

The rate of acceleration is proportional to the strength of the electric field, and inversely proportional to the mass of the particle. The particle can not continue to accelerate forever however. Since it is located within a solid, sooner or later it will collide with either another carrier, or perhaps one of the fixed atoms within the solid. We will assume that the collision is completely inelastic, and that after a collision, the particle comes to a stop, only to be accelerated again by the electric field. If we were to make a plot of the particles velocity as a function of time, it might look something like Figure 1.3.

**Figure 1.3:** Velocity as a function of time for charge carrier

Although the particle achieves various velocities, depending upon how much time there is between collisions, there will be some average velocity,  $\overline{v}$ , which will depend upon the details of the collision process.

Let us define a scattering time  $\tau_s$  which will give us that average velocity when we multiply it times the acceleration of the particle. That is:

$$\bar{v} = \frac{qE\tau_s}{m} \tag{1.7}$$

or

$$\tau_s \equiv \frac{m \, \bar{v}}{qE} \tag{1.8}$$

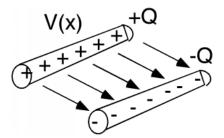

Now let's take a look at just a small section of the conductor (Figure 1.4). It will have the cross section of the sample, A, but will only be  $\bar{v}$   $\Delta(t)$  long, where  $\Delta(t)$  is just some arbitrary time interval.

Figure 1.4: Section of the conductor

After a time  $\Delta(t)$  has passed, all of the charges within the box will have left it, as they are all moving with the same average velocity,  $\bar{v}$ . If the density of charge carriers in the conductor is n per unit volume, then the number of carriers N within our little box is just n times the volume of the box  $\bar{v}$   $\Delta(t)$  A

$$N = n \ \overline{v} \ \Delta(t) A \tag{1.9}$$

Thus the total charge, Q, which leaves the box in time  $\Delta(t)$  is just qN. The current flow, I, is just the amount of charge which flows out of the box per unit time

$$I = \frac{qn\overline{v}\Delta(t)A}{\Delta(t)}$$

$$= qn\overline{v}A$$

$$= \frac{q^2n\tau_sEA}{m}$$

$$= \frac{Q}{\Delta(t)}$$

(1.10)

We now have two choices, we can look at our result from a field quantity point of view, in which case we will be interested in the **current density**, J, which is just the current, I, divided by the cross-sectional area

$$J = \frac{I}{A}$$

$$= \frac{q^2 n \tau_s}{m} E$$

$$= \sigma E$$

(1.11)

where  $\sigma$  is called the **conductivity** of the material. If we look at the conductor from a macroscopic point of view, then we are interested in the relationship between the voltage and the current. The voltage is just

the electric field times the length of the sample, and the current is just the current density times is cross sectional area. Thus we have

$$I = AJ$$

$$= A\sigma E$$

$$= A\sigma \frac{V}{L}$$

(1.12)

or

$$V = \frac{L}{\sigma A}I$$

$$= RI$$

(1.13)

where R is the resistance of the sample. We have discovered **Ohm's law**!

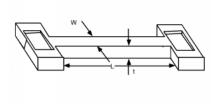

Note that (1.13) tells us that the resistance of the sample is proportional to its length (the longer the sample, the higher the resistance) and inversely proportional to its cross sectional area (the fatter the sample, the lower the resistance). The sample resistance is also inversely proportional to the conductivity  $\sigma$  of the sample. Sometimes, instead of conductivity, the **resistivity**,  $\rho$ , is specified for a resistive material. The resistivity is simply the inverse of the conductivity

$$\sigma = \frac{1}{\rho} \tag{1.14}$$

and thus:

$$R = \frac{\rho L}{A} \tag{1.15}$$

And, in an effort towards completeness, there is one other quantity which you might run into, and that is the carrier **mobility**,  $\mu$ . The mobility is just the proportionality factor between the average velocity of the particle and the electric field. That is:

$$\bar{v} = \mu E \tag{1.16}$$

You should check that the following two relationships are correct:

$$\sigma = nq\mu \tag{1.17}$$

$$\mu = \frac{q\tau_s}{m} \tag{1.18}$$

If we take an ordinary conductor (and we will have to define later what we mean by that) and heat it up, the atoms within the material start to vibrate faster due to the elevated temperature, and the carriers suffer significantly more collisions. The mean collision time  $\tau_s$  decreases, and hence the conductivity goes down, and the resistance of the sample goes up.

#### 1.2 Introduction to Semiconductors<sup>2</sup>

If we only had to worry about simple conductors, life would not be very complicated, but on the other hand we wouldn't be able to make computers, CD players, cell phones, i-Pods and a lot of other things which we have found to be useful. We will now move on, and talk about another class of conductors called semiconductors.

In order to understand semiconductors and in fact to get a more accurate picture of how metals, or normal conductors actually work, we really have to resort to quantum mechanics. Electrons in a solid are very tiny objects, and it turns out that when things get small enough, they no longer exactly following the classical "Newtonian" laws of physics that we are all familiar with from everyday experience. It is not the purpose of this course to teach you quantum mechanics, so what we are going to do instead is describe the

<sup>&</sup>lt;sup>2</sup>This content is available online at <a href="http://cnx.org/content/m1001/2.13/">http://cnx.org/content/m1001/2.13/</a>.

results which come from looking at the behavior of electrons in a solid from a quantum mechanical point of view.

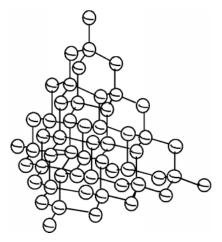

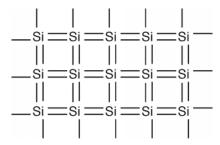

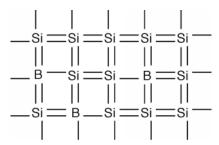

Solids (at least the ones we will be talking about, and especially semiconductors) are crystalline materials, which means that they have their atoms arranged in a ordered fashion. We can take silicon (the most important semiconductor) as an example. Silicon is a group IV element, which means it has four electrons in its outer or valence shell. Silicon crystallizes in a structure called the **diamond** crystal lattice. This is shown in Figure 1.5. Each silicon atom has four covalent bonds, arranged in a tetrahedral formation about the atom center.

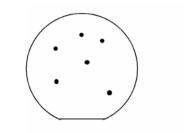

Figure 1.5: Crystal structure of silicon

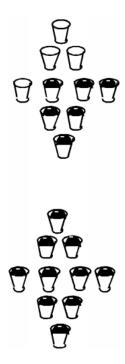

In two dimensions, we can schematically represent a piece of single-crystal silicon as shown in Figure 1.6. Each silicon atom shares its four valence electrons with valence electrons from four nearest neighbors, filling the shell to 8 electrons, and forming a stable, periodic structure. Once the atoms have been arranged like this, the outer valence electrons are no longer strongly bound to the host atom. The outer shells of all of the atoms blend together and form what is called a **band**. The electrons are now free to move about within this band, and this can lead to electrical conductivity as we discussed earlier.

Figure 1.6: A 2-D representation of a silicon crystal

This is not the complete story however, for it turns out that due to quantum mechanical effects, there is not just one band which holds electrons, but several of them. What will follow is a very qualitative picture of how the electrons are distributed when they are in a periodic solid, and there are necessarily some details which we will be forced to gloss over. On the other hand this will give you a pretty good picture of what is

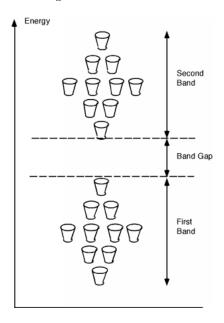

going on, and may enable you to have some understanding of how a semiconductor really works. Electrons are not only distributed throughout the solid crystal spatially, but they also have a distribution in energy as well. The potential energy function within the solid is periodic in nature. This potential function comes from the positively charged atomic nuclei which are arranged in the crystal in a regular array. A detailed analysis of how electron **wave functions**, the mathematical abstraction which one must use to describe how small quantum mechanical objects behave when they are in a periodic potential, gives rise to an energy distribution somewhat like that shown in Figure 1.7.

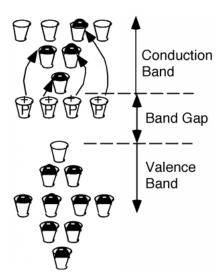

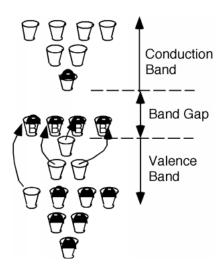

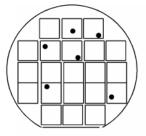

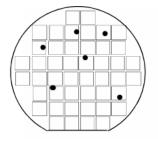

Figure 1.7: Schematic of the first two bands in a periodic solid showing energy levels and bands

Firstly, unlike the case for free electrons, in a periodic solid, electrons are not free to take on any energy value they wish. They are forced into specific energy levels called **allowed states** which are represented by the cups in the figure. The allowed states are not distributed uniformly in energy either. They are grouped into specific configurations called **energy bands**. There are no allowed levels at zero energy and for some distance above that. Moving up from zero energy, we then encounter the first energy band. At the bottom of the band there are very few allowed states, but as we move up in energy, the number of allowed states first increases, and then falls off again. We then come to a region with no allowed states, called an energy **band gap**. Above the band gap, another band of allowed states exists. This goes on and on, with any given material having many such bands and band gaps. This situation is shown schematically in Figure 1.7, where the small cups represent allowed energy levels, and the vertical axis represents electron energy.

It turns out that each band has exactly 2N allowed states in it, where N is the total number of atoms in the particular crystal sample we are talking about. (Since there are 10 cups in each band in the figure, it must represent a crystal with just 5 atoms in it. Not a very big crystal at all!) Into these bands we must now distribute all of the valence electrons associated with the atoms, with the restriction that we can **only put one electron into each allowed state**. (This is the result of something called the **Pauli exclusion principle**.) Since in the case of silicon there are 4 valence electrons per atom, we would **just** fill up the first two bands, and the next would be empty. (If we make the logical assumption that the electrons will fill in the levels with the lowest energy first, and only go into higher lying levels if the ones below are already filled.) This situation is shown in Figure 1.8.

Here, we have represented electrons as small black balls with a "-" sign on them. Indeed, the first two

bands are completely full, and the next is empty. What will happen if we apply an electric field to the sample of silicon? Remember the diagram we have at hand right now is an **energy** based one, we are showing how the electrons are distributed in energy, not how they are arranged spatially. On this diagram we can not show how they will move about, but only how they will change their energy as a result of the applied field. The electric field will exert a force on the electrons and attempt to accelerate them. If the electrons are accelerated, then they must increase their kinetic energy. Unfortunately, there are no empty allowed states in either of the filled bands. An electron would have to jump all the way up into the next (empty) band in order to take on more energy. In silicon, the gap between the top of the highest most occupied band and the lowest unoccupied band is 1.1 eV. (One eV is the potential energy gained by an electron moving across an electrical potential of one volt.) The **mean free path** or distance over which an electron would normally move before it suffers a collision is only a few hundred angstroms ( $\approx (300 \times 10^{-8})$  cm) and so you would need a very large electric field (several hundred thousand  $\frac{\text{volts}}{\text{cm}}$ ) in order for the electron to pick up enough energy to "jump the gap". This makes it appear that silicon would be a very bad conductor of electricity, and in fact, very pure silicon is very poor electrical conductor.

Figure 1.8: Silicon, with first two bands full and the next empty

A metal is an element with an **odd** number of valence electrons so that a metal ends up with an upper band which is just half full of electrons. This is illustrated in Figure 1.9. Here we see that one band is full, and the next is just half full. This would be the situation for the Group III element aluminum for instance. If we apply an electric field to these carriers, those near the top of the distribution can indeed move into higher energy levels by acquiring some kinetic energy of motion, and easily move from one place to the next. In reality, the whole situation is a bit more complex than we have shown here, but this is not too far from how it actually works.

Figure 1.9: Electron distribution for a metal or good conductor

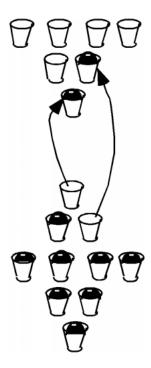

So, back to our silicon sample. If there are no places for electrons to "move" into, then how does silicon work as a "semiconductor"? Well, in the first place, it turns out that not all of the electrons are in the bottom two bands. In silicon, unlike say quartz or diamond, the band gap between the top-most full band, the next empty one is not so large. As we mentioned above it is only about 1.1 eV. So long as the silicon is not at absolute zero temperature, some electrons near the top of the full band can acquire enough thermal energy that they can "hop" the gap, and end up in the upper band, called the **conduction band**. This situation is shown in Figure 1.10.

Figure 1.10: Thermal excitation of electrons across the band gap

In silicon at room temperature, roughly  $10^{10}$  electrons per cubic centimeter are thermally excited across the band-gap at any one time. It should be noted that the excitation process is a continuous one. Electrons are being excited across the band, but then they fall back down into empty spots in the lower band. On average however, the  $10^{10}$  in each cm<sup>3</sup> of silicon is what you will find at any given instant. Now 10 billion electrons per cubic centimeter **seems** like a lot of electrons, but lets do a simple calculation. The mobility of electrons in silicon is about  $1000 \, \frac{\text{cm}^2}{\text{volt-sec}}$ . Remember, mobility times electric field yields the average velocity of the carriers. Electric field has units of  $\frac{\text{volts}}{\text{cm}}$ , so with these units we get velocity in  $\frac{\text{cm}}{\text{sec}}$  as we should.) The charge on an electron is  $1.6 \times 10^{-19}$  coulombs. Thus from this equation (1.17):

$$\sigma = nq\mu

= 10^{10} (1.6 \times 10^{-19}) 1000

= 1.6 \times 10^{-6} \frac{\text{mhos}}{\text{cm}}$$

(1.19)

If we have a sample of silicon 1 cm long by (1mm) (1mm) square, it would have a resistance of

$$R = \frac{L}{\sigma A}$$

$$= \frac{1}{(1.6 \times 10^{-6})0.1^{2}}$$

$$= 62.5M\Omega$$

(1.20)

which does not make it much of a "conductor". In fact, if this were all there was to the silicon story, we could pack up and move on, because at **any** reasonable temperature, silicon would conduct electricity very poorly.

### 1.3 Doped Semiconductors<sup>3</sup>

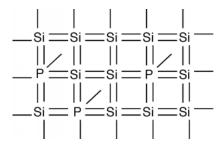

To see how we can make silicon a useful electronic material, we will have to go back to its crystal structure. Suppose somehow (and we will talk about how this is done later) we could substitute a few atoms of phosphorus for some of the silicon atoms.

Figure 1.11: A silicon crystal "doped" with phosphorus

If you sneak a look at the periodic table, you will see that phosphorus is a group V element, as compared with silicon which is a group IV element. What this means is the phosphorus atom has five outer or valence electrons, instead of the four which silicon has. In a lattice composed mainly of silicon, the extra electron associated with the phosphorus atom has no "mating" electron with which it can complete a shell, and so is left loosely dangling to the phosphorus atom, with relatively low binding energy. In fact, with the addition of just a little thermal energy (from the natural or latent heat of the crystal lattice) this electron can break free and be left to wander around the silicon atom freely. In our "energy band" picture, we have something like what we see in Figure 1.12. The phosphorus atoms are represented by the added cups with P's on them. They are new allowed energy levels which are formed within the "band gap" near the bottom of the first empty band. They are located close enough to the empty (or "conduction") band, so that the electrons which they contain are easily excited up into the conduction band. There, they are free to move about and contribute to the electrical conductivity of the sample. Note also, however, that since the electron has left the vicinity of the phosphorus atom, there is now one more proton than there are electrons at the atom, and hence it has a net positive charge of 1 q. We have represented this by putting a little "+" sign in each P-cup. Note that this positive charge is fixed at the site of the phosphorous atom called a **donor** since it "donates" an electron up into the conduction band, and is not free to move about in the crystal.

<sup>&</sup>lt;sup>3</sup>This content is available online at <a href="http://cnx.org/content/m1002/2.15/">http://cnx.org/content/m1002/2.15/</a>.

Figure 1.12: Silicon doped with phosphorus

How many phosphorus atoms do we need to significantly change the resistance of our silicon? Suppose we wanted our 1 mm by 1 mm square sample to have a resistance of one ohm as opposed to more than  $60 \text{ M}\Omega$ . Turning the resistance equation around we get

$$\sigma = \frac{L}{RA}$$

$$= \frac{1\Omega}{1 \times 0.1^2}$$

$$= 100 \frac{\text{mho}}{\text{cm}}$$

(1.21)

And hence (If we continue to assume an electron mobility of  $1000 \frac{\text{cm}^2}{\text{voltsec}}$

$$n = \frac{\sigma}{q\mu}$$

$$= \frac{100}{(1.6 \times 10^{-19})1000}$$

$$= 6.25 \times 10^{17} \text{cm}^3$$

(1.22)

Now adding more than  $6 \times 10^{17}$  phosphorus atoms per cubic centimeter might seem like a lot of phosphorus, until you realize that there are almost  $10^{24}$  silicon atoms in a cubic centimeter and hence only one in every 1.6 million silicon atoms has to be changed into a phosphorus one to reduce the resistance of the sample from several 10s of  $M\Omega$  down to only one  $\Omega$ . This is the real power of semiconductors. You can make dramatic changes in their electrical properties by the addition of only minute amounts of impurities. This process is called "doping" the semiconductor. It is also one of the great challenges of the semiconductor manufacturing industry, for it is necessary to maintain fantastic levels of control of the impurities in the material in order to predict and control their electrical properties.

Again, if this were the end of the story, we still would not have any calculators, stereos or "Agent of Doom" video games (Or at least they would be very big and cumbersome and unreliable, because they would have to work using vacuum tubes!). We now have to focus on the few "empty" spots in the lower, almost full band (Called the **valence band**.) We will take another view of this band, from a somewhat different perspective. I must confess at this point that what I am giving you is even further from the way things really work, then the "cups at different energies" picture we have been using so far. The problem is, that in order to do things right, we have to get involved in momentum phase-space, a lot more quantum mechanics, and

generally a bunch of math and concepts we don't really need in order to have some idea of how semiconductor devices work. What follow below is really intended as a motivation, so that you will have some feeling that what we state as results, is actually reasonable.

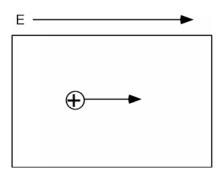

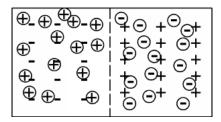

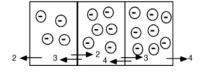

Consider Figure 1.13. Here we show all of the electrons in the valence, or almost full band, and for simplicity show one missing electron. Let's apply an electric field, as shown by the arrow in the figure. The field will try to move the (negatively charged) electrons to the left, but since the band is almost completely full, the only one that can move is the one right next to the empty spot, or **hole** as it is called.

Figure 1.13: Band full of electrons, with one missing

One thing you may be worrying about is what happens to the electrons at the ends of the sample. This is one of the places where we are getting a somewhat distorted view of things, because we should really be looking in momentum, or wave-vector space rather than "real" space. In that picture, they magically drop off one side and "reappear" on the other. This doesn't happen in real space of course, so there is no easy way we can deal with it.

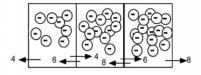

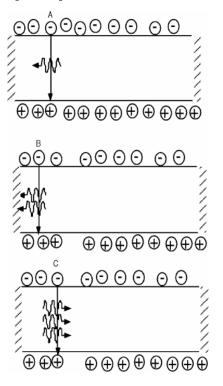

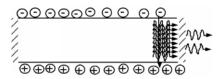

A short time after we apply the electric field we have the situation shown in Figure 1.14, and a little while after that we have Figure 1.15. We can interpret this motion in two ways. One is that we have a net flow of negative charge to the left, or if we consider the effect of the aggregate of all the electrons in the band (which we have to do because of quantum mechanical considerations beyond the scope of this book) we could picture what is going on as a single positive charge, moving to the right. This is shown in Figure 1.16. Note that in either view we have the same net effect in the way the total **net** charge is transported through the sample. In the mostly negative charge picture, we have a net flow of negative charge to the left. In the single positive charge picture, we have a net flow of positive charge to the right. Both give the same sign for the current!

Figure 1.14: Motion of the "missing" electron with an electric field

Figure 1.15: Further motion of the "missing electron" spot

Figure 1.16: Motion of a "hole" due to an applied electric field

Thus, it turns out, we can consider the consequences of the empty spaces moving through the co-ordinated motion of electrons in an almost full band as being the motion of positive charges, moving wherever these empty spaces happen to be. We call these charge carriers "holes" and they too can add to the total conduction of electricity in a semiconductor. Using  $\rho$  to represent the density (in cm<sup>-3</sup> of spaces in the valence band

and  $\mu_e$  and  $\mu_h$  to represent the mobility of electrons and holes respectively (they are usually not the same) we can modify this equation (1.17) to give the conductivity  $\sigma$ , when both electrons' holes are present.

$$\sigma = nq\mu_e + \rho q\mu_h \tag{1.23}$$

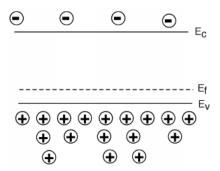

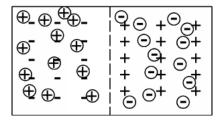

How can we get a sample of semiconductor with a **lot** of holes in it? What if, instead of phosphorus, we dope our silicon sample with a group III element, say boron? This is shown in Figure 1.17. Now we have some **missing** orbitals, or places where electrons could go if they were around. This modifies our energy picture as follows in Figure 1.18. Now we see a set of new levels introduced by the boron atoms. They are located within the band gap, just a little way above the top of the almost full, or valence band. Electrons in the valence band can be thermally excited up into these new allowed levels, creating empty states, or holes, in the valence band. The excited electrons are stuck at the boron atom sites called **acceptors**, since they "accept" an electron from the valence band, and hence act as **fixed** negative charges, localized there. A semiconductor which is doped predominantly with acceptors is called **p-type**, and most of the electrical conduction takes place through the motion of holes. A semiconductor which is doped with donors is called **n-type**, and conduction takes place mainly through the motion of electrons.

Figure 1.17: Silicon doped with Boron

Figure 1.18: P-type silicon, due to boron acceptors

In n-type material, we can assume that all of the phosphorous atoms, or **donors**, are fully ionized when they are present in the silicon structure. Since the number of donors is usually much greater than the native,

or intrinsic electron concentration, ( $\approx (10^{10} \text{cm}^{-3})$ ), if  $N_d$  is the density of donors in the material, then n, the electron concentration,  $\approx (N_d)$ .

If an electron deficient material such as boron is present, then the material is called **p-type** silicon, and the hole concentration is just  $p \simeq N_a$  the concentration of **acceptors**, since these atoms "accept" electrons from the valence band.

If both donors and acceptors are in the material, then which ever one has the higher concentration wins out. (This is called **compensation**.) If there are more donors than acceptors then the material is n-type and  $n \simeq N_d - N_a$ . If there are more acceptors than donors then the material is p-type and  $p \simeq N_a - N_d$ . It should be noted that in most compensated material, one type of impurity usually has a much greater (several order of magnitude) concentration than the other, and so the subtraction process described above usually does not change things very much. (  $10^{18} - 10^{16} \simeq 10^{18}$ ).

One other fact which you might find useful is that, again, because of quantum mechanics, it turns out that the **product** of the electron and hole concentration in a material must remain a constant. In silicon at room temperature:

$$np \equiv n_i^2 \simeq 10^{20} \text{cm}^{-3}$$

(1.24)

Thus, if we have an n-type sample of silicon doped with  $10^{17}$  donors per cubic centimeter, then n, the electron concentration is just and p, the hole concentration, is  $\frac{10^{20}}{10^{17}} = 10^3 \text{cm}^{-3}$ . The carriers which dominate a material are called **majority carriers**, which would be the electrons in the above example. The other carriers are called **minority carriers** (the holes in the example) and while  $10^3$  might not seem like much compared to  $10^{17}$  the presence of minority carriers is still quite important and can not be ignored. Note that if the material is undoped, then it must be that n=p and  $n=p=10^{10}$ .

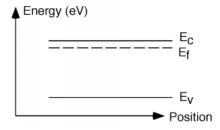

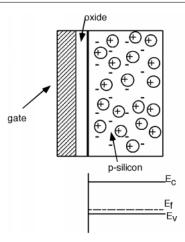

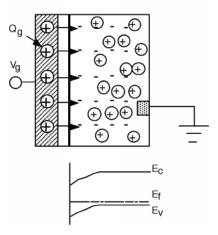

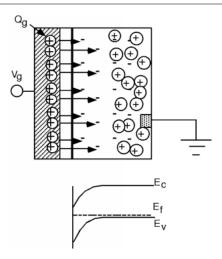

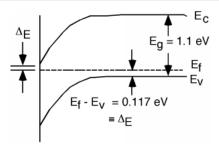

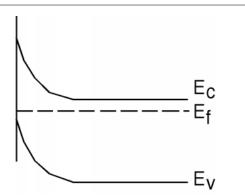

The picture of "cups" of different allowed energy levels is useful for gaining a pictorial understanding of what is going on in a semiconductor, but becomes somewhat awkward when you want to start looking at devices which are made up of both n and p type silicon. Thus, we will introduce one more way of describing what is going on in our material. The picture shown in Figure 1.19 is called a band diagram. A band diagram is just a representation of the energy as a function of position with a semiconductor device. In a band diagram, positive energy for electrons is upward, while for holes, positive energy is downwards. That is, if an electron moves upward, its potential energy increases just as a with a normal mass in a gravitational field. Also, just as a mass will "fall down" if given a chance, an electron will move down a slope shown in a band diagram. On the other hand, holes gain energy by moving downward and so they have a tendancy to "float" upward if given the chance - much like a bubble in a liquid. The line labeled  $E_e$  in Figure 1.19 shows the edge of the conduction band, or the bottom of the lowest unoccupied allowed band, while  $E_v$  is the top edge of the valence, or highest occupied band. The band gap,  $E_g$  for the material is obviously  $E_c - E_v$ . The dotted line labeled  $E_f$  is called the **Fermi level** and it tells us something about the chemical equilibrium energy of the material, and also something about the type and number of carriers in the material. More on this later. Note that there is no zero energy level on a diagram such as this. We often use either the Fermi level or one or other of the band edges as a reference level on lieu of knowing exactly where "zero energy" is located.

Figure 1.19: An electron band-diagram for a semiconductor

The distance (in energy) between the Fermi level and either  $E_c$  and  $E_v$  gives us information concerning the density of electrons and holes in that region of the semiconductor material. The details, once again, will have to be begged off on grounds of mathematical complexity. (Take Semiconductor Devices (ELEC 462) in your senior year and find out how is really works!) It turns out that you can say:

$$n = N_c e^{-\frac{E_c - E_f}{kT}} \tag{1.25}$$

$$p = N_v e^{-\frac{E_f - E_v}{kT}} \tag{1.26}$$

Both  $N_c$  and  $N_v$  are constants that depend on the material you are talking about, but are typically on the order of  $10^{19} {\rm cm}^{-3}$ . The expression in the denominator of the exponential is just Boltzman's constant, k, times the temperature T of the material (in absolute temperature or Kelvin). Boltzman's constant  $k = (8.63 \times 10^{-5}) \frac{{\rm eV}}{K}$ . At room temperature kT = 1/40 of an electron volt. Look carefully at the numerators in the exponential. Note first that there is a minus sign in front, which means the bigger the number in the exponent, the fewer carriers we have. Thus, the top expression says that if we have n-type material, then  $E_f$  must not be too far away from the conduction band, while if we have p-type material, then the Fermi level,  $E_f$  must be down close to the valence band. The closer  $E_f$  gets to  $E_c$  the more electrons we have. The closer  $E_f$  gets to  $E_v$ , the more holes we have. Figure 1.19 therefore must be for a sample of n-type material. Note also that if we know how heavily a sample is doped (That is, we know what  $N_d$  is for example) and from the fact that  $n \simeq N_d$  we can use (1.25) to find out how far away the Fermi level is from the conduction band

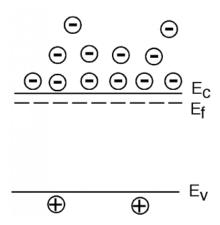

$$E_c - E_f = kT \ln\left(\frac{N_c}{N_d}\right) \tag{1.27}$$

To help further in our ability to picture what is going on, we will often add to this band diagram, some small signed circles to indicate the presence of mobile electrons and holes in the material. Note that the electrons are spread out in energy. From our "cups" picture we know they like to stay in the lower energy states if possible, but some will be distributed into the higher levels as well. What is distorted here is the scale. The band-gap for silicon is 1.1 eV, while the **actual** spread of the electrons would probably only be a few tenths of an eV, not nearly as much as is shown in Figure 1.20. Lets look at a sample of p-type material, just for comparison. Note that for holes, increasing energy goes **down** not up, so their distribution is inverted from that of the electrons. You can kind of think of holes as bubbles in a glass of soda or beer, they want to float to the top if they can. Note also for both n and p-type material there are also a few "minority" carriers, or carriers of the opposite type, which arise from thermal generation across the band-gap.

Figure 1.20: Band diagram for an n-type semiconductor

#### 1.4 P-N Junction: Part I<sup>4</sup>

Figure 1.21: Band diagram for a p-type semiconductor

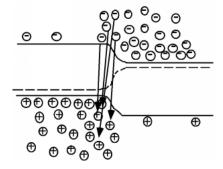

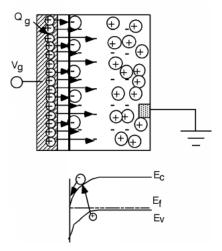

Figure 1.22: A non-equilibrium p-n junction

We are now ready to make an actual useful device! Let's take a piece of n-type material, and a piece of p-type material, and stick them together, as shown in Figure 1.22. This way we will be making a **pn-junction**, or **diode**, which will be our first real electric device other than a simple resistor.

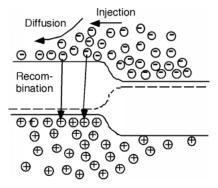

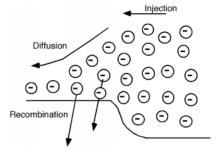

There are a couple of things wrong with Figure 1.22. First of all, one of the rules regarding the Fermi level is that when you have a system at **equilibrium** (that is, when it is a rest, and is not being influenced by external forces such as thermal gradients, electrical potentials etc.), the Fermi level must be the same everywhere. Secondly, we have a big bunch of holes on the right and a big bunch of electrons on the left, and so we would expect, that in the absence of some force to keep them this way, they will start to spread out until their distribution is more or less equal everywhere. Finally, we remember that a hole is just an absence of an electron, and since an electron in the conduction band can lower the system energy by falling down into one of the empty hole states, it seems likely that this will happen. This process is called **recombination**. The place where this is most likely to occur, of course, would be right at the junction between the n and p regions. This is shown in Figure 1.23.

$<sup>^4{</sup>m This\ content\ is\ available\ online\ at\ < http://cnx.org/content/m1003/2.13/>.}$

Figure 1.23: Recombination of holes and electrons

Now is might seem that this recombination effect might just go on and on, until there are no carriers left in the sample. This is not the case however. In order to see what brings everything to a halt, we need yet another diagram. Figure 1.24 is more physical than what we have been looking at so far. It is a picture of the actual p-n junction, showing both the holes and the electrons. We also need to put in the donors and acceptors however, if we want to see what goes on. The fixed (can't move around) charges of the donors and acceptors are represented by simple "+" and "-" signs. They are arranged in a nice lattice-like arrangement to remind us that they are stuck to the crystal lattice. (In reality however, even though they are stuck in the crystal lattice, there are so few of them compared to the silicon atoms that their distribution would be quite random.) For the mobile holes and electrons, we will stay with the little circles with charge signs in them. These are randomly distributed, to remind us that they are free to move about the crystal.

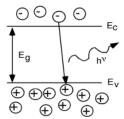

Figure 1.24: Spatial schematic of a p-n junction

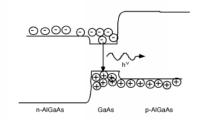

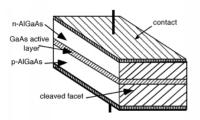

We will now have to allow some of the holes and electrons (again near the junction) to recombine. Remember, when an electron and a hole recombine, they both are annihilated and disappear. Note that this process conserves charge (and if we could calculate it) momentum as well. There is obviously some energy lost, but this will simply show up as vibrations, or heat, within the crystal lattice. Or, in the case of an LED, as light emitted from the device. See, already we know enough about semiconductors to understand (somewhat) how an actual device works. Light comming from an LED is simply the energy which is realeased when an electron and hole recombine. We will take a look at this in more detail later. Let's allow some recombination to occur, as shown in Figure 1.25.

Figure 1.25: The junction after some recombination has occurred

And then in Figure 1.26 some more.....

Figure 1.26: After further recombination

#### 1.5 PN-Junction: Part II<sup>5</sup>

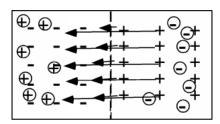

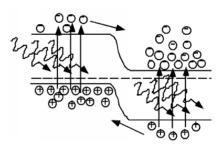

If you look closely at these pictures, you will notice something. As we remove more and more electrons and holes, we are starting to "uncover" the fixed charges associated with the donors and acceptors. We are making what is known as a **depletion region**, so named because it is **depleted** of mobile carriers (holes and electrons). The uncovered net charge in the depletion region is separated, with negative charge in the p-region, and positive charge in the n-region. What will such a charge separation give rise to? Why, an electric field! Of course! Which way will the field point? The electric field which arises from a separation of charges always goes from the positive charge, towards the negative charge. This is shown in Figure 1.27.

Figure 1.27: The pn-junction with the resultant built-in electric field

<sup>&</sup>lt;sup>5</sup>This content is available online at <a href="http://cnx.org/content/m1004/2.14/">http://cnx.org/content/m1004/2.14/</a>.

What effect will this field have on our device? It will have the tendency to push the holes back into the p-region and the electrons into the n-region. This is just what we need to counteract the recombination which has been going on, and hopefully bring it to a stop.

Now try to think through what effect this field could have on our energy band diagram. The band diagram is for electrons, so if an electron moves from the right hand side of the device (the n-region) towards the left hand side (the p-region), it will have to move through an electric field which is opposing its motion. This means it has do some work, or in other words, the potential energy for the electron must go up. We can show this on the band diagram by simply shifting the bands on the left hand side upward, to indicate that there is a shift in potential energy as electrons move from right to left across the junction.

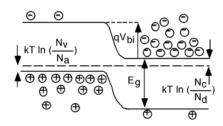

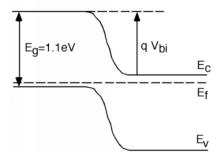

Figure 1.28: Energy band diagram for a p-n junction at equilibrium

The shift of the bands, which is just the difference between the location of the Fermi level in the n-region and the Fermi level is the p-region, is called the **built-in potential**,  $V_{\rm bi}$ . This built-in potential keeps the majority of holes in the p-region, and the electrons in the n-region. It provides a potential barrier, which prevents current flow across the junction. (On the band diagram we have to multiply the built-in potential  $V_{\rm bi}$  by the charge of an electron, q, so that we can represent the shift in energy in terms of **electron volts**, the unit of potential energy used in band diagrams.)

How big is  $V_{\text{bi}}$ ? This is not too hard to figure out. Let's look at Figure 1.28 a little more carefully. Remember, we know from this equation (1.25) and this equation (1.26) that since  $n = N_d$  in the n-region and  $p = N_a$  in the p-region, we can relate the distance of the Fermi level from  $E_c$  and  $E_f$  by

$$E_c - E_f = kT \ln\left(\frac{N_c}{N_d}\right) \tag{1.28}$$

and

$$E_f - E_v = kT \ln\left(\frac{N_v}{N_a}\right) \tag{1.29}$$

Look at Figure 1.28 and see if you can agree that

$$qV_{\text{BI}} = E_g - (E_c - E_f) - (E_f - E_v)$$

$$= E_g - kT \ln\left(\frac{N_c}{N_d}\right) - kT \ln\left(\frac{N_c}{N_d}\right)$$

$$= E_g - kT \ln\left(\frac{N_c N_v}{N_d N_a}\right)$$

(1.30)

Where  $N_d$  and  $N_a$  are the doping densities in the n and p sinc respectively. Remember, kT = 1/40 eV = 0.025 eV,  $E_q = 1.1 \text{eV}$  and  $N_c$  and  $N_v$  are both  $\approx (10^{19})$ . Thus,

$$qV_{\rm BI} = 1.1 {\rm eV} - 0.025 {\rm eV ln} \left( \frac{10^{38}}{N_d N_a} \right)$$

Here the q in front of the  $V_{\rm BI}$  and the e in eV are both the charge of 1 electron and they cancel out making

$$V_{\rm BI} = \left(1.1 - 0.025 \ln\left(\frac{10^{38}}{N_d N_a}\right)\right) \text{volts}$$

Suppose both  $N_d$  and  $N_a$  are both about [10 to the 15th] - not uncommon values. How big would the built-in potential be in this case?

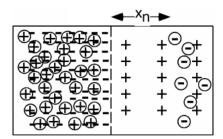

It turns out that we can actually derive some specific details about the depletion region if we make only a coupled of simplifying (and often justified) assumptions. In order to make the math easier, and also because many p-n junctions are built this way, we will consider what is known as a **one sided junction**. Figure 1.29 is a picture of such a beast: In this diode, one side is much more heavily doped than the other. In this particular example, the p-side is heavily doped, and the n-side is relatively lightly doped. We can not show the true picture here, because typically, the more heavily doped side will be doped **several orders of magnitude** greater than the lightly doped side. Typical values might be  $N_a = 10^{19}$  and  $N_d = 10^{16}$ . Regardless of how big the difference is however, there must be exactly the same amount of "uncovered" charge on both side of the junction. Why? Because each time a hole and electron recombine to form the depletion region, they each leave behind either a donor or an acceptor. A careful count of the exposed charge in Figure 1.29 shows that I was careful enough to draw my figure accurately for you. We do not need to have a one-sided diode to do the analysis that will follow, but the equations are easier to solve if we do.

Figure 1.29: An example of a one-sided diode

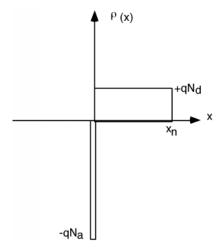

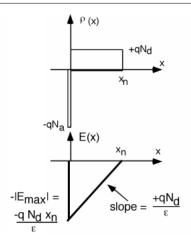

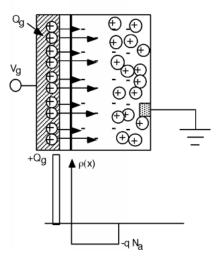

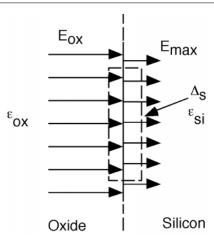

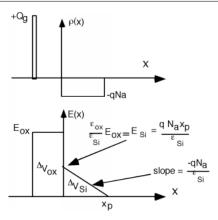

In order to proceed from here, the first thing we do is make a plot of the charge density  $\rho(x)$  as we move through the junction. Naturally, in the bulk, since the holes and the acceptors (in the p-side), or the electrons and the donors (in the n-side) just equal one another, the net charge density is zero. In the depletion region, the charge density is -  $(-q) N_a$  on the p-side and  $(q) N_d$  on the donor side. (All the mobile carriers are gone, and we are left with just the charged acceptors or donors.) We will make the assumption that on the n-side, the depletion extends a distance  $-x_n$  from the junction. On the p-side, the acceptor charge density is so large, that we will treat it is a  $\delta$ -function, with essentially no width. The areas of the two boxes must be the same (equal amount of positive and negative charge) and hence, the tall thin box actually has a width of  $\frac{N_d}{N_a}x_n$ , which, since  $N_a$  is several orders of magnitude greater than  $N_d$ , means that the tall box has a very very small width compared to the lower, wider one, which is  $qN_d$  tall, and has a width of  $x_n$ .

Figure 1.30: Charge density as a function of position

#### 1.6 Gauss' Law<sup>6</sup>

Now we have to review some field theory. We will be using fields from time to time in this course, and when we need some aspect of field theory, we will introduce what we need at that point. This seems to make more sense than spending several weeks talking about a lot of abstract theory without seeing how or why it can be useful.

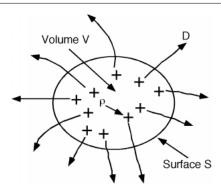

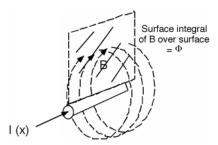

The first thing we need to remember is **Gauss' Law**. Gauss' Law, like most of the fundamental laws of electromagnetism comes not from first principle, but rather from empirical observation and attempts to match experiments with some kind of self-consistent mathematical framework. Gauss' Law states that:

$$\oint DdS = Q_{\text{encl}}$$

$$= \oint_{v} \rho(v) dV$$

(1.31)

where D is the **electric displacement vector**, which is related to the **electric field vector**, E, by the relationship  $D = \epsilon E$ .  $\epsilon$  is called the **dielectric constant**. In silicon it has a value of  $1.1 \times 10^{-12} \frac{F}{\rm cm}$ . (Note that D must have units of  $\frac{\text{Coulombs}}{\text{cm}^2}$  to have everything work out OK.)  $Q_{\rm encl}$  is the total amount of charge enclosed in the volume V, which is obtained by doing a volume integral of the charge density  $\rho(v)$ .

<sup>&</sup>lt;sup>6</sup>This content is available online at <a href="http://cnx.org/content/m1005/2.15/">http://cnx.org/content/m1005/2.15/</a>.

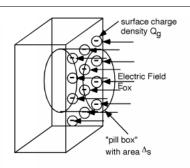

Figure 1.31: Pictorial representation of Gauss' Law.

(1.31) just says that if you add up the surface integral of the displacement vector D over a closed surface S, what you get is the sum of the total charge enclosed by that surface. Useful as it is, the integral form of Gauss' Law, (which is what (1.31) is) will not help us much in understanding the details of the depletion region. We will have to convert this equation to its differential form. We do this by first shrinking down the volume V until we can treat the charge density  $\rho(v)$  as a constant  $\rho$ , and replace the volume integral with a simple product. Since we are making V small, let's call it  $\Delta(V)$  to remind us that we are talking about just a small quantity.

$$\oint_{\Delta(v),} \rho(v) dV \to \rho \Delta(v)$$

(1.32)

And thus, Gauss' Law becomes:

$$\oint DdS = \epsilon \oint EdS$$

$$= \rho \Delta (V)$$

(1.33)

or

$$\frac{1}{\Delta(V)} \left( \oint_{s_{i}} E dS \right) = \frac{\rho}{\epsilon} \tag{1.34}$$

Now, by **definition** the limit of the LHS of (1.34) as  $\Delta(V) \to 0$  is known as the divergence of the vector E, div(E). Thus we have

$$\lim_{\Delta(V)\to 0} \frac{1}{\Delta(V)} \left( \oint_{s_{i}} E dS \right) = div(E)$$

$$= \frac{\varrho}{\epsilon} \tag{1.35}$$

Note what this says about the divergence. The divergence of the vector E is the limit of the surface integral of E over a volume V, normalized by the volume itself, as the volume shrinks to zero. I like to think of as a kind of "point surface integral" of the vector E.

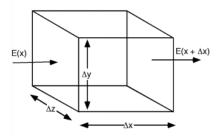

Figure 1.32: Small volume for divergence

If E only varies in one dimension, which is what we are working with right now, the expression for the divergence is particularly simple. It is easy to work out what it is from a simple picture. Looking at Figure 1.32 we see that if E is only pointed along one direction (let's say x) and is only a function of x, then the surface integral of E over the volume  $\Delta(V) = \Delta(x) \Delta(y) \Delta(z)$  is particularly easy to calculate.

$$\oint_{s} EdS = E(x + \Delta(x)) \Delta(y) \Delta(z) - E(x) \Delta(y) \Delta(z) \tag{1.36}$$

Where we remember that the surface integral is defined as being positive for an outward pointing vector and negative for one which points into the volume enclosed by the surface. Now we use the definition of the divergence

$$div(E) = \lim_{\Delta(V) \to 0} \frac{1}{\Delta(V)} \left( \oint_{s} E dS \right)$$

$$= \lim_{\Delta(V) \to 0} \frac{(E(x + \Delta(x)) - E(x))\Delta(y)\Delta(z)}{\Delta(x)\Delta(y)\Delta(z)}$$

$$= \lim_{\Delta(V) \to 0} \frac{E(x + \Delta(x)) - E(x)}{\Delta(x)}$$

$$= \frac{\partial E(x)}{\partial x}$$

$$(1.37)$$

So, we have for the differential form of Gauss' law:

$$\frac{\partial E\left(x\right)}{\partial x} = \frac{\rho\left(x\right)}{\epsilon} \tag{1.38}$$

Thus, in our case, the rate of change of E with x,  $\frac{d}{dx}(E)$ , or the **slope of** E(x) is just equal to the charge density,  $\rho(x)$ , divided by  $\epsilon$ .

## 1.7 Depletion Width<sup>7</sup>

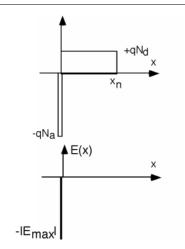

We can now go back to the charge density as a function of position graph (Figure 1.30) and easily find the electric field in the depletion region as a function of position. If we integrate Gauss' Law (1.38), we get for the electric field:

$$E(x) = \frac{1}{\epsilon} \int \rho(x) dx$$

(1.39)

$<sup>^7\</sup>mathrm{This}$  content is available online at  $<\!\mathrm{http://cnx.org/content/m1006/2.16/}\!>$ .

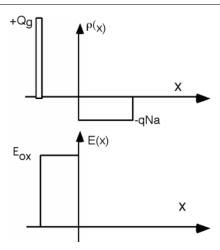

We **could** write down an expression for  $\rho(x)$  and then formally integrate it to get E(x) but we can also just do it graphically, which is a lot easier, and gives us a much more intuitive feeling for what is going on. Let's start doing our integral at [x equals -infinity] Whenever we perform an integral such as (1.39), we've got to remember to add a constant to our answer. Since we can not have an electric field which extends to infinity (either plus or minus) however, we can safely assume E(-infinity) = 0 and remains at that value until we get to the edge of the depletion region at (essentially) x equals zero. Since the charge density is zero all the way up to the edge of depletion region, Gauss tells us that the electric field can not change here either. When we get to x=0 we encounter the large negative delta-function of negative charge at the edge of the depletion region. If you can remember back to your calculus, when you integrate a delta function, you get a step. Since the charge in the p-side delta function is negative, when we integrate it, we get a negative step. Since we don't know (yet) how big the step will be, let's just call it -|Emax|.

Figure 1.33: Finding the electric field in the p-type region

Figure 1.34: Finishing the integral

In the n-side of the depletion region

$$\rho(x) = (q) N_d

= \epsilon \frac{\partial E}{\partial x}$$

(1.40)

and so we plot E(x) with a (positive) slope of  $\frac{qN_d}{\epsilon}$ , starting at E(x) = -Emax at x = 0. This line continues with this positive slope until it reaches a value of 0 at  $x = x_n$ . We know that E(x) must equal 0 at  $x = x_n$  because there is no further charge outside of the depletion region and E(x) must be 0 outside this region.

We are now done doing the integral. We would know everything about this problem, if we just knew what  $x_n$  was. Note that since we know the slope of the triangle now, we can find  $-E_{\text{max}}$  in terms of the slope and  $x_n$ . We can derive an expression for  $x_n$ , if we remember that the integral of the electric field over a distance is the potential drop across that distance. What is the potential drop in going from the p-side to the n-side of the diode?

As a reminder, Figure 1.35 shows the junction band diagram again. The potential drop must just be  $V_{\rm bi}$  the "built-in" potential of the junction. Obviously  $V_{\rm bi}$  can not be greater than 1.1 V, the band-gap potential. On the other hand, by looking at Figure 1.35, and remembering that the bandgap in silicon is 1.1 eV, it will not be some value like 0.2 or 0.4 volts either. Let's make life easy for ourselves, and say  $V_{\rm bi} = 1$ Volt. This will not be too far off, and as you will see shortly, the answer is not very sensitive to the **exact** value of  $V_{\rm bi}$  anyway.

Figure 1.35: Band diagram for a p-n junction

The integral of E(x) is now just the area of the triangle in Figure 1.34. Getting the area is easy:

area =

$$\frac{1}{2}$$

base × height

=  $1/2x_n \frac{qN_dx_n}{\epsilon}$

=  $\frac{qN_dx_n^2}{2\epsilon}$

=  $V_{\text{bi}}$  (1.41)

We can simply turn (1.41) around and solve for  $x_n$ .

$$x_n = \sqrt{\frac{2\epsilon V_{\text{bi}}}{qN_d}} \tag{1.42}$$

As we said, for silicon,  $\epsilon_{Si}=1.1\times 10^{-12}$ . Let's let  $N_d=10^{16} {\rm cm}^{-3}$  donors. As we already know from before,  $q=1.6\times 10^{-19}$  Coulombs. This makes  $x_n=3.7\times 10^{-5} {\rm cm}$  or 0.37  $\mu {\rm m}$  long. Not a very wide depletion region! How big is  $|E_{\rm max}|$ ? Plugging in

$$E_{\text{max}} = \frac{qN_dx_n}{\epsilon} \tag{1.43}$$

We find  $|E_{\text{max}}| = 53,000 \frac{V}{\text{cm}}!$  Why such a big electric field? Well, we've got to shift the potential by about a volt, and we do not have much distance to do it in (less than a micron), and so there must be, by default, a fairly large field in the depletion region. Remember, potential is electric field **times** distance.

Enough p-n junction electrostatics. The point of this exercise was two-fold; a): so you would know something about the details of what is really going on in a p-n junction; b): to show you that with just some very simple electrostatics and a little thinking, it is not so hard to figure these things out!

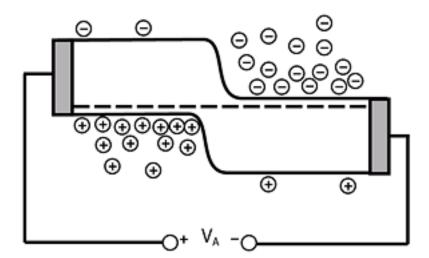

#### 1.8 Forward Biased<sup>8</sup>

Now let's take a look at what happens when we apply an external voltage to this junction. First we need some conventions. We make connections to the device using **contacts**, which we show as cross-hatched blocks. These contacts allow the free passage of current into and out of the device. Current usually flows through wires in the form of electrons, so it is easy to imagine electrons flowing into or out of the n-region. In the p-region, when electrons flow **out** of the device **into** the wire, holes will flow into the p-region (so as to maintain continuity of current through the contact.) When electrons flow into the p-region, they will recombine with holes, and so we have the net effect of holes flowing out of the p-region.

<sup>&</sup>lt;sup>8</sup>This content is available online at <a href="http://cnx.org/content/m1007/2.19/">http://cnx.org/content/m1007/2.19/</a>.

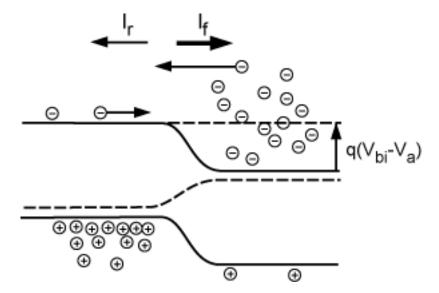

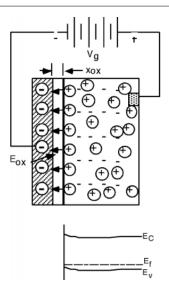

Figure 1.36: A p-n diode with contacts and external bias

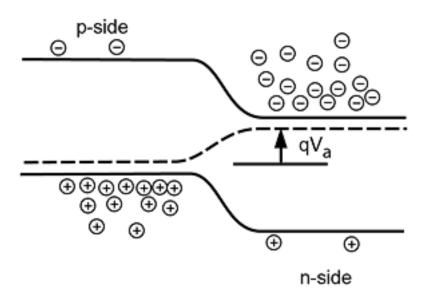

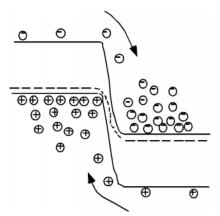

With the convention that a **positive applied voltage** means that the terminal connected to the p-region is positive with respect to the terminal connected to the n-region. This is easy to remember; "p is positive, n is negative". Let us try to figure out what will happen when we apply a positive applied voltage  $V_a$ . If  $V_a$  is positive, then that means that the potential energy for electrons on the p-side must be **lower** than it was under the equilibrium condition. We reflect this on the band diagram by **lowering** the bands on the p-side from where they were originally. This is shown in Figure 1.37.

Figure 1.37: A p-n junction under forward bias

As we can see from Figure 1.37, when the p-region is lowered a couple of things happen. First of all, the Fermi level (the dotted line) is no longer a flat line, but rather it bends upward in going from the p-region to the n-region. The amount it bends (and hence the amount of shift of the bands) is just given by  $qV_a$ , where the energy scale we are using for the band diagram is in **electron-volts** which, as we said before, is a common measure of potential energy when we are talking about electronic materials. The other thing we can notice is that the electrons on the n-side and the holes on the p-side now "see" a lower potential energy barrier than they saw when no voltage was applied. In fact, it looks as if a lot of electrons now have sufficient energy such that they could move across from the n-region and flow into the p-region. Likewise, we would expect to see holes moving across from the p-region into the n-region.

This flow of carriers across the junction will result in a current flow across the junction. In order to see how this current will behave with applied voltage, we have to use a result from statistical thermodynamics concerning the distribution of electrons in the conduction band, and holes in the valence band. We saw from our "cups" analogy, that the electrons tend to fill in the lowest states first, with fewer and fewer of them as we go up in energy. For most situations, a very good description of just how the electrons are distributed in energy is given by a simple exponential decay. (This comes about from a statistical analysis of electrons, which belong to a class of particles called **Fermions**. Fermions have the properties that they are: a): indistinguishable from one another; b): obey the **Pauli Exclusion Principle** which says that two Fermions can not occupy the same exact **state** (energy and spin); c): remain at some fixed total number N.)

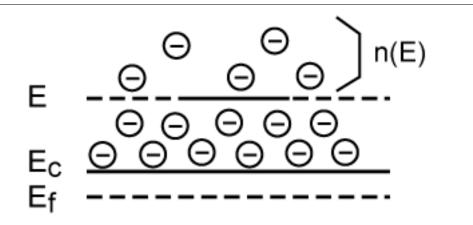

If n(E) tells us how many electrons there are with an energy greater than some value  $E_c$  then n(E) is given simply as:

$$n\left(E\right) = N_{d}e^{-\frac{E-E_{c}}{kT}}\tag{1.44}$$

The expression in the denominator is just Boltzman's constant times the temperature in Kelvins. At room temperature kT has a value of about 1/40 of an eV or 25 meV. This number is sometimes called the **thermal** voltage,  $V_T$ , but it's ok for you to just think of it as a constant which comes from the thermodynamics of

the problem. Because  $kT \simeq 1/40$ , you will sometimes see (1.44) and similar equations written as

$$n(E) = N_d e^{-40(E - E_c)} (1.45)$$

Which looks a little strange if you forget where the 40 came from, and just see it sitting there.

If the energy E is  $E_c$  the energy level of the conduction band, then  $n(E_c) = N_d$ , the density of electrons in the n-type material. As E increases above  $E_c$ , the density of electrons falls off exponentially, as depicted schematically in Figure 1.38: Now let's go back to the unbiased junction.

Figure 1.38: Distribution of electrons in the conduction band with energy

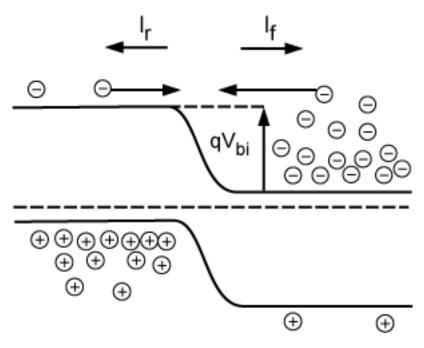

Remember, as we said before, there are currents flowing across the junction, even if there is no bias. The current we have shown as  $I_f$  is due to those electrons which have an energy greater than the built-in potential. They are flowing from right to left, as shown by the open arrow, which, of course, gives a current flowing from left to right, as shown by the solid arrows. Based on (1.44) the current should be proportional to:

$$I_f \propto N_d e^{-\frac{qV_{\rm bi}}{kT}} \tag{1.46}$$

Figure 1.39: Balanced flow across a junction

The principle of detailed balance says that at zero bias,  $I_f = -I_r$  and so

$$I_R \propto -\left(N_d e^{-\frac{qV_{\rm bi}}{kT}}\right) \tag{1.47}$$

$$I_R = (-(I_f \alpha)) - N_d e^{-\frac{qV_{\text{BI}}}{kT}}$$

(1.48)

Now, what happens when we apply the bias? For the electrons over on the n-side, the barrier has been reduced from a height of  $qV_{\rm bi}$  to  $q(V_{\rm bi}-V_a)$  and hence the forward current will be significantly increased.

$$I_f \propto N_d e^{-\frac{q(V_{\rm bi} - V_a)}{kT}} \tag{1.49}$$

The reverse current however, will remain just the same as it was before (1.47).

Figure 1.40: Current when the junction is forward biased

The total current across the junction is just  $I_f + I_r$

$$N_d \left( e^{\frac{qV_a}{kT}} - 1 \right) \tag{1.50}$$

where we have factored out the  $N_d e^{-\frac{qV_{\rm bi}}{kT}}$  term out of both expressions. We are not prepared, with what we know at this point, to get the other terms in the proportionality that are involved here. Also, the astute reader will note that we have not said anything about the holes, but it should be obvious that they will also contribute to the current, and the arguments we have made for electrons will hold for the holes just as well.

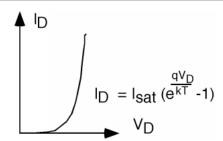

We can take the effect of the holes, and the other unknowns about the proportionality, and bind them all into one constant called  $I_{\text{sat}}$ , so that we write:

$$I = I_{\text{sat}} \left( e^{\frac{qV_a}{kT}} - 1 \right) \tag{1.51}$$

This is the famous **diode equation** and is a very important result.

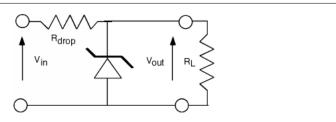

# 1.9 The Diode Equation<sup>9</sup>

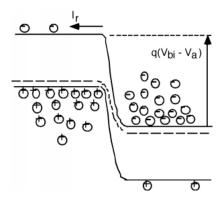

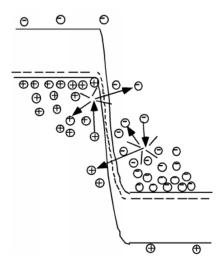

The reason for calling the proportionality constant  $I_{\rm sat}$  will become obvious when we consider reverse bias. Let us now make  $V_a$  negative instead of positive. The applied electric field now adds in the same direction to the built-in field. This means the barrier will increase instead of decrease, and so we have what is shown in Figure 1.41. Note that we have marked the barrier height as  $q(V_{\rm bi} - V_a)$  as before. It is just that now,  $V_a$  is negative, and so the barrier is bigger.

<sup>&</sup>lt;sup>9</sup>This content is available online at <a href="http://cnx.org/content/m1008/2.17/">http://cnx.org/content/m1008/2.17/</a>.

Figure 1.41: P-N junction under reverse bias ( $V_a < 0$ )

Remember, the electrons fall off exponentially as we move up in energy, so it does not take much of a shift of the bands before there are essentially **no** electrons on the n-side with enough energy to get over the barrier. This is reflected in the diode equation (1.51) where, if we let  $V_a$  be a negative number,  $e^{\frac{qV_a}{kT}}$  very quickly goes to zero and we are left with

$$I = -I_{\text{sat}} \tag{1.52}$$

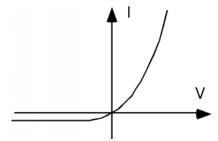

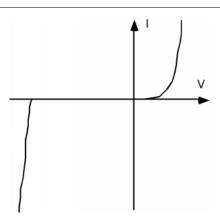

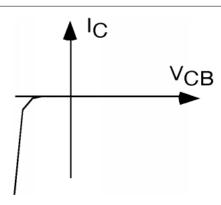

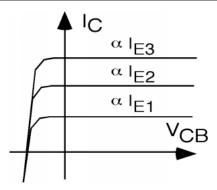

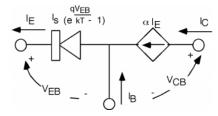

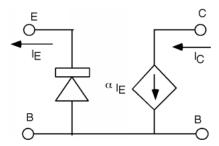

Thus, while in the forward bias direction, the current increases exponentially with voltage, in the reverse direction it simply saturates at  $-I_{\text{sat}}$ . A plot of I as a function of voltage or an **I-V** characteristic curve might look something like Figure 1.42.

Figure 1.42: Idealized I-V curve for a p-n diode

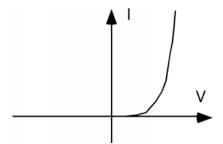

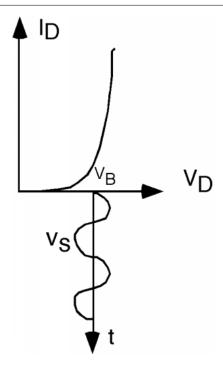

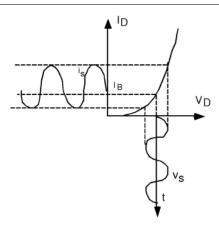

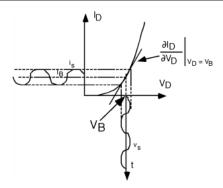

In fact, for **real diodes** (ones made from silicon)  $I_{\rm sat}$  is such a small value (on the order of  $10^{-10}$  amps) that you can not even see it on most common measuring devices (oscilloscope, digital volt meter etc.) and if you were to look on a device called a **curve tracer** (which you will learn more about in Electronic Circuits [ELEC 342]) what you would really see would be something like Figure 1.43.

Figure 1.43: Realistic I-V curve

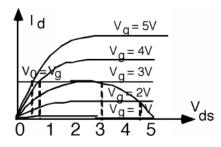

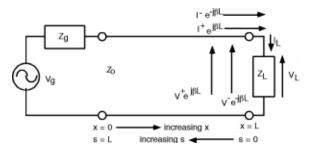

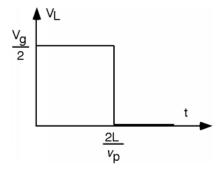

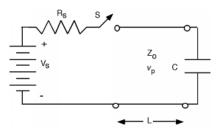

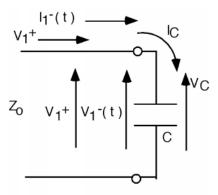

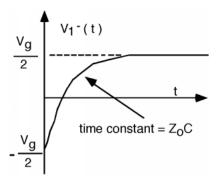

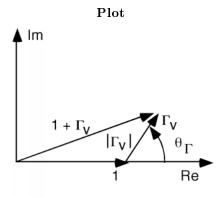

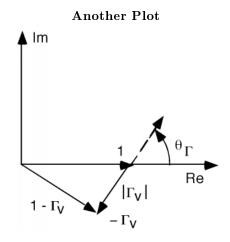

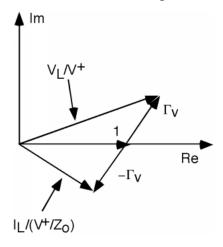

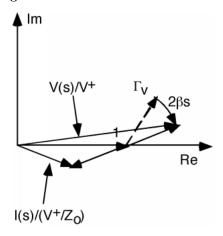

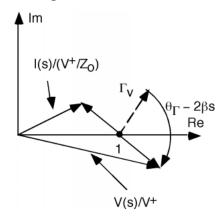

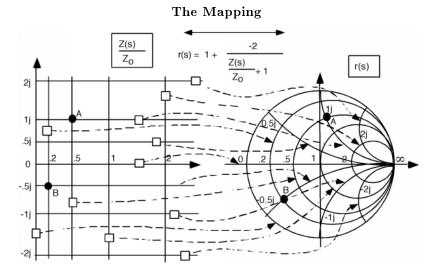

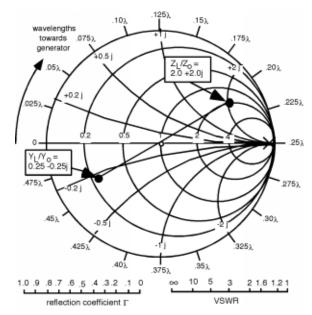

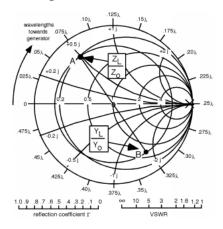

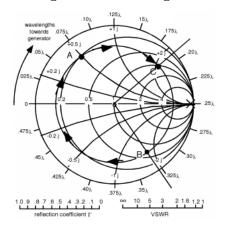

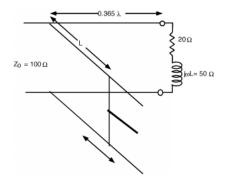

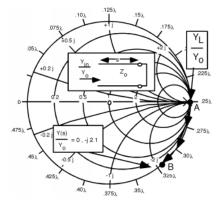

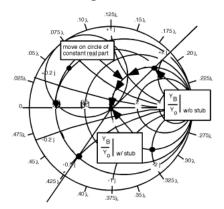

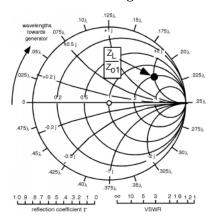

We see what looks like zero current in the reverse direction, and in fact, what appears to be no current until we get a certain amount of voltage across the diode, after which it very quickly "turns on" with a very rapidly increasing forward current. For silicon, this "turn on" voltage is about 0.6 to 0.7 volts.